Порівняльний аналіз baseband-процесорів для реалізації SDR-трансиверів

Основний зміст сторінки статті

Анотація

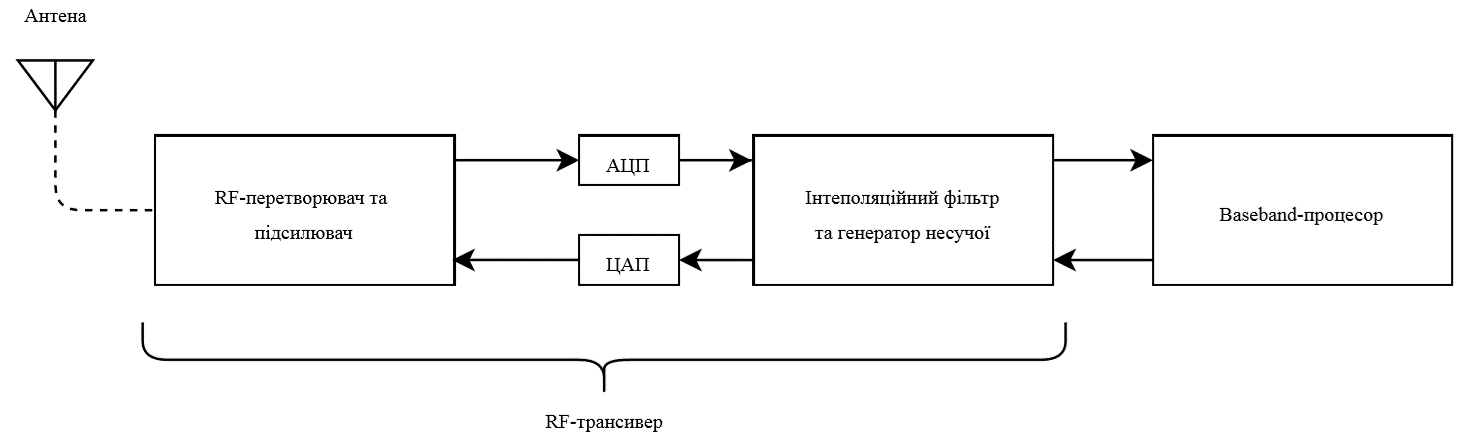

Проведено порівняльний аналіз обчислювальних засобів для їх подальшого використання у ролі baseband-процесору для трансивера типу Software Defined Radio. Встановлено, що для цієї ролі можна використати процесори загального користування у парі з графічними процесорами, що мають високу гнучкість у проектуванні, але низьку швидкодію та високе енергоспоживання. Використання спеціальних процесорів обробки сигналів надає перевагу у кращому енергоспоживанні, що надає можливість використовувати їх для швидкої розробки портативних трансиверів з достатньо низкою ціною. Для високопродуктивних трансиверів краще за все використовувати програмовані логічні інтегральні схеми, що за рахунок високого паралелізму надують суттєвий виграш у швидкодії. Запропонована власна архітектура трансивера з використанням системи-на-кристалі та радіочастотного трансивера для побудови гнучкої системи передачі інформації по безпровідному каналу зв’язку.

Блок інформації про статтю

Ця робота ліцензується відповідно до Creative Commons Attribution 4.0 International License.

Автори, які публікуються у цьому журналі, погоджуються з наступними умовами:- Автори залишають за собою право на авторство своєї роботи та передають журналу право першої публікації цієї роботи на умовах ліцензії Creative Commons Attribution License, котра дозволяє іншим особам вільно розповсюджувати опубліковану роботу з обов'язковим посиланням на авторів оригінальної роботи та першу публікацію роботи у цьому журналі.

- Автори мають право укладати самостійні додаткові угоди щодо неексклюзивного розповсюдження роботи у тому вигляді, в якому вона була опублікована цим журналом (наприклад, розміщувати роботу в електронному сховищі установи або публікувати у складі монографії), за умови збереження посилання на першу публікацію роботи у цьому журналі.

- Політика журналу дозволяє і заохочує розміщення авторами в мережі Інтернет (наприклад, у сховищах установ або на особистих веб-сайтах) рукопису роботи, як до подання цього рукопису до редакції, так і під час його редакційного опрацювання, оскільки це сприяє виникненню продуктивної наукової дискусії та позитивно позначається на оперативності та динаміці цитування опублікованої роботи (див. The Effect of Open Access).

Посилання

“RF Agile Transceiver AD9361,” Analog Devices. p. 36, 2016, URL:http://www.analog.com/static/imported-files/data_sheets/AD9361.pdf.

A. Haghighat, “A review on essentials and technical challenges of software defined radio,” in MILCOM 2002. Proceedings, 2002, pp. 377–382, DOI: 10.1109/MILCOM.2002.1180471.

M. Galloy, “CPU vs GPU performance,” 2011. [Online]. Available:https://michaelgalloy.com/2013/06/11/cpu-vs-gpu-performance.html.

M. Vestias and H. Neto, “Trends of CPU, GPU and FPGA for high-performance computing,” in 2014 24th International Conference on Field Programmable Logic and Applications (FPL), 2014, pp. 1–6, DOI: 10.1109/FPL.2014.6927483.

K. Li, M. Wu, G. Wang, and J. R. Cavallaro, “A high performance GPU-based software-defined basestation,” in 2014 48th Asilomar Conference on Signals, Systems and Computers, 2014, pp. 2060–2064, DOI: 10.1109/ACSSC.2014.7094835.

S. A. Dyer and B. K. Harms, “Digital Signal Processing,” in Advances in Computers, Elsevier, 1993, pp. 59–117, URL: https://linkinghub.elsevier.com/retrieve/pii/S0065245808604039.

A. Gatherer, T. Stetzler, M. McMahan, and E. Auslander, “DSP-based architectures for mobile communications: past, present and future,” IEEE Commun. Mag., vol. 38, no. 1, pp. 84–90, 2000, DOI: 10.1109/35.815456.

D. Strenski, C. Kulkarni, J. Cappello, and P. Sundararajan, “Latest FPGAs Show Big Gains in Floating Point Performance.” [Online]. Available: https://www.hpcwire.com/2012/04/16/latest_fpgas_show_big_gains_in_floating_point_performance/.

S. Kestur, J. D. Davis, and O. Williams, “BLAS Comparison on FPGA, CPU and GPU,” in 2010 IEEE Computer Society Annual Symposium on VLSI, 2010, pp. 288–293, DOI: 10.1109/ISVLSI.2010.84.

K. Underwood, “FPGAs vs. CPUs: trends in peak floating-point performance,” in Proceeding of the 2004 ACM/SIGDA 12th international symposium on Field programmable gate arrays - FPGA ’04, 2004, p. 171, DOI: 10.1145/968280.968305.

“MATLAB HDL Coder Generate code from MATLAB code,” MATLAB. [Online]. Available: https://www.mathworks.com/products/hdl-coder.html.

“ZedBoardTM is a low-cost development board for the Xilinx Zynq®-7000 All Programmable SoC.” ZedBoard, URL: http://zedboard.org/sites/default/files/product_briefs/5066-PB-AES-Z7EV-7Z020-G-V3c %281%29_0.pdf.

“Library for interfacing with Linux IIO devices,” Analog Devices Iinc. Analog Devices Iinc, URL: https://github.com/analogdevicesinc/libiio.