Генератор QR-коду на основі FPGA

Основний зміст сторінки статті

Анотація

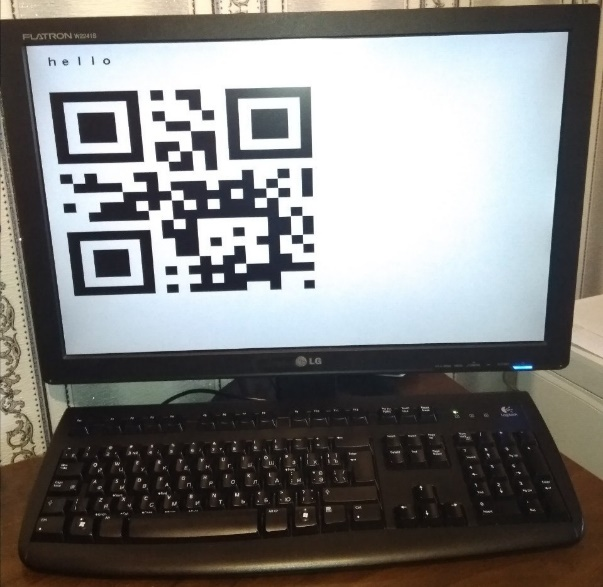

Розроблено апаратне IP-ядро для генерування QR-кодів на ПЛІС, що підтримує першу версію кодів з корекцією помилок M типу. На основі розробленого IP-ядра, на платі налагодження DE1-SoC створено макетний зразок пристрою для генерування QR-кодів. Зазначений пристрій дозволяє за допомогою клавіатури з інтерфейсом PS/2 вводити текстові дані, які мають бути зашифровані у QR-коді та виводити результат (згенерований код) на VGA монітор у вигляді зображення. Для створення такого пристрою використовується модуль керування, IP-блок для генерування QR-кодів та модулі введення-виведення.

Блок інформації про статтю

Ця робота ліцензується відповідно до Creative Commons Attribution 4.0 International License.

Автори, які публікуються у цьому журналі, погоджуються з наступними умовами:- Автори залишають за собою право на авторство своєї роботи та передають журналу право першої публікації цієї роботи на умовах ліцензії Creative Commons Attribution License, котра дозволяє іншим особам вільно розповсюджувати опубліковану роботу з обов'язковим посиланням на авторів оригінальної роботи та першу публікацію роботи у цьому журналі.

- Автори мають право укладати самостійні додаткові угоди щодо неексклюзивного розповсюдження роботи у тому вигляді, в якому вона була опублікована цим журналом (наприклад, розміщувати роботу в електронному сховищі установи або публікувати у складі монографії), за умови збереження посилання на першу публікацію роботи у цьому журналі.

- Політика журналу дозволяє і заохочує розміщення авторами в мережі Інтернет (наприклад, у сховищах установ або на особистих веб-сайтах) рукопису роботи, як до подання цього рукопису до редакції, так і під час його редакційного опрацювання, оскільки це сприяє виникненню продуктивної наукової дискусії та позитивно позначається на оперативності та динаміці цитування опублікованої роботи (див. The Effect of Open Access).

Посилання

"Generator QR codov [Генератор QR кодов]," [Online]. Available: http://qrcoder.ru/. [Accessed 15 03 2020].

"Pochemu nam stoit prismotret'sya k QR-kodam v 2019 godu [Почему нам стоит присмотреться к QR-кодам в 2019 году]," [Online]. Available: https://lifehacker.ru/qr-kody-v-2019-godu/. [Accessed 15 03 2020].

"PLIS (FPGA) i mikrokontroller. V chem raznitsa? [ПЛИС (FPGA) и микроконтроллер. В чем разница?]," [Online]. Available: http://micro-proger.ru/2016/03/17/plis-fpga-i-mikrokontroller-v-chem-raznica/. [Accessed 15 03 2020].

"Verilog Language ," [Online]. Available: https://en.wikipedia.org/wiki/Verilog. [Accessed 15 03 2020].

"ASCII," [Online]. Available: https://en.wikipedia.org/wiki/ASCII. [Accessed 15 03 2020].

"Algoritm generatsii QR-koda [Алгоритм генерации QR-кода]," [Online]. Available: https://habr.com/ru/post/172525/. [Accessed 15 03 2020].

K. Kasperski, "Polinomial'naya arifmetika i polya Galua, ili Informatsiya, voskresshaya iz pepla [Полиноминальная арифметика и поля Галуа, или информация, воскрешая из пепла]," Sistemniy administrator, p. 84–90, 2003.

"Wounded QR codes," [Online]. Available: http://datagenetics.com/blog/november12013/index.html. [Accessed 15 03 2020].

"Algoritmy raspoznavaniya graficheskogo markera [Алгоритм распознавания графического маркера]," [Online]. Available: https://studbooks.net/2238811/informatika/algoritmy_raspoznavaniya_graficheskogo_markera. [Accessed 15 03 2020].

Terasic DE1-SoC User Manual, 2014, p. pp. 30–33.